概 要

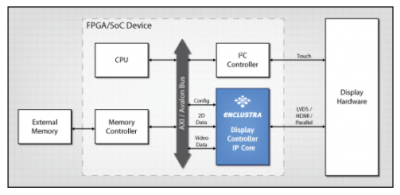

モジュール設計と強力なスケーラビリティを備えたDisplay Controller IP Coreは、FPGAリソースを無駄にすることなく、システム要件に完全に適合します。これらのユニークな機能は、将来のプロジェクトでのディスプレイコントローラIPコアの再利用も簡素化します。現在または将来のプロジェクトのディスプレイ制御ニーズに合わせて当社のディスプレイコントローラIPコアを選択することにより、製品化までの時間およびシステム全体のコストを大幅に削減できます。

ハイライト

・ 外部ディスプレイコントローラデバイスなしのパラレル、LVDS、およびHDMI / DVIディスプレイのサポート

・ 無制限のビデオページのサポート

・ ディスプレイ輝度制御用の内蔵PWMジェネレータ

・ オプションの2Dアクセラレータユニット(描画/コピー矩形、透明色サポート)

・ レジスタバンクとフレームバッファメモリアクセスの両方に対応するAXI / Avalonバスインタフェース

利 点

・ 外部ディスプレイコントローラデバイスが不要で、PCBが小さくなり、部品点数が削減

・ モジュラー設計によるリソース使用率の低下と優れたスケーリング

・ 統合バスインタフェースと明確にレイアウトされたレジスタバンクにより容易に統合

特 徴

・ サポートされているカラーモード

- 16ビットトゥルーカラー(5/6/5)

- 24ビットトゥルーカラー

・ サポートされているディスプレイ解像度:

- 低コストのFPGAで最大1280×1024 *

- 高性能FPGA上の1920×1080 *1

*1 これらの解像度は参考用であり保証されていないことに注意してください。達成可能な最大の分解能は、メモリ帯域幅、クロック周波数などのシステム設計要因に依存する。

ご提供

・ ディスプレイコントローラIPコア

- VHDLソースファイル(製品オプションに応じてプレーンまたは暗号化)

- リファレンスデザイン

- ユーザーマニュアル

・ ディスプレイコントローラIPコアリファレンスデザイン

- リファレンスデザインのトップレベルVHDLファイル(プレーンVHDL)

- UCF / XDC / SDC制約ファイル(製品オプションによる)

- ザイリンクスISE /ザイリンクスVivado™/インテル®Quartus®プロジェクトファイル(製品オプションに依存)

- トップレベルのシミュレーションテストベンチファイル(プレーンVHDL)

- トップレベルシミュレーションModelSimプロジェクトファイル

- ドキュメンテーション