概 要

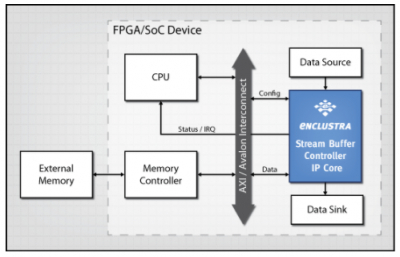

IPコアは、各ストリームの動作モード、バッファサイズ、およびバッファアドレスに関して高度に構成可能である。コンフィギュレーションは、エンベデッドCPU、FPGAマネージャー・アプリケーション、またはVHDLのアプリケーション固有のストリーム・コンフィグレーター・コントローラーのいずれかによって、メモリー・マップされたスレーブ・インターフェースを介して行われます。

ハイライト

IPコアは、各チャネルに対して4つの異なる動作モードをサポートしています。

・ FIFOモード:メモリへの書き込みと読み出しは、AXI4-Streamインタフェースを介して行われます

・ 書き込みモード:メモリへの書き込みはAXI4-Streamを介して行われ、メモリからの読み出しはCPUによって行われます。

・ 読み出しモード:メモリへの書き込みはCPUによって行われ、メモリからの読み出しはAXI4-Streamインタフェースを介して行われます。

・ ROMモード:メモリからの読み出しは、AXI4-Streamインタフェースを介して行われます。メモリは、最初にCPUによって書き込まれなければならない

利 点

・ 書き込みおよび読み出しデータストリームのデータ幅変換をサポート

・ 異なる動作モードを使用することにより、単一のIPコアで多用途のアプリケーションを実現可能

・ 統合バスインタフェースと明確にレイアウトされたレジスタバンクにより容易に統合

・ CPUを必要としないスタンドアロンのソリューションは、VHDLで提供されているストリーム構成コントローラによって容易に実現可能

特 徴

・ 最大16の書き込みおよび読み出しストリームをサポート(製品オプションに依存)

・ 書き込みおよび読み取りパスの設定可能なステータスフラグ

・ ベンダーに依存しない実装

・ AvalonまたはAMBA-AXIインターフェイスで使用可能

・ 任意のバイト幅に/からのデータ幅変換

ご提供

・ ストリームバッファコントローラIPコア

- VHDLソースファイル(製品オプションに応じてプレーンまたは暗号化)

- リファレンスデザイン

- ユーザーマニュアル

・ ストリームバッファコントローラAPI

- Cソースコード

- アプリケーションソフトウェアの例

- ユーザーマニュアル

・ ストリームバッファコントローラIPコアリファレンスデザイン

- リファレンスデザインのトップレベルVHDLファイル(プレーンVHDL)

- UCF / XDC / SDC制約ファイル(製品オプションによる)

- ザイリンクスISE /ザイリンクスVivado™/インテル®Quartus®プロジェクトファイル(製品オプションに依存)

- トップレベルのシミュレーションテストベンチファイル(プレーンVHDL)

- トップレベルシミュレーションModelSimプロジェクトファイル

- ドキュメンテーション